100G LR1 SFP56-DD 광 트랜시버는 단일 모드 광섬유(SMF)를 통해 최대 10km 거리의 100기가비트 이더넷 링크에 사용하도록 설계되었습니다. 이 제품은 SFP56-DD MSA, IEEE802.3CU, 100G Lambda 100G LR1 및 100GAUI-2(FEC 없음)1 표준을 준수합니다. SFP56-DD MSA에 명시된 대로 I2C 인터페이스를 통해 디지털 진단 기능을 사용할 수 있습니다.

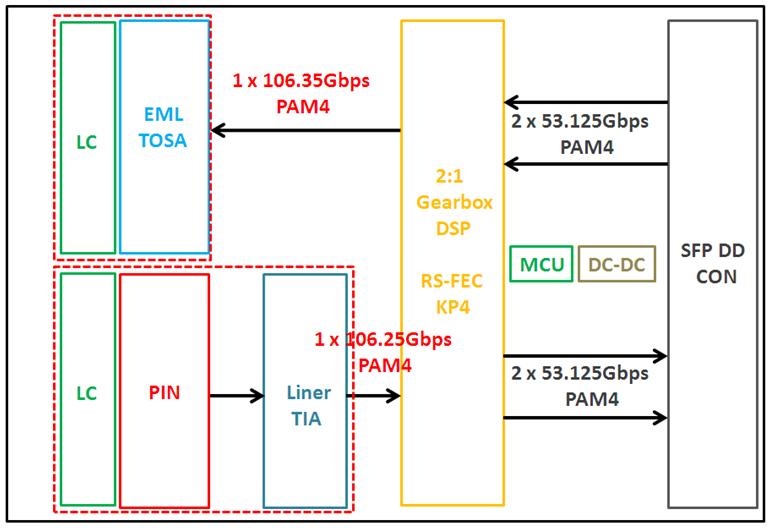

이 모듈은 1311nm 중심 파장에서 100Gbps 데이터 전송 속도로 동작하는 1채널 광 신호를 포함합니다. 이 모듈은 53Gbps(PAM4) 전기 입력 데이터 2채널을 106Gbps(PAM4) 광 신호 1채널로 변환할 수 있으며, 또한 106Gbps(PAM4) 광 신호 1채널을 53Gbps(PAM) 전기 출력 데이터 2채널로 변환할 수 있습니다. 광 인터페이스는 듀플렉스 LC 커넥터를 사용합니다. 고성능 냉각형 EML 송신기와 고감도 PIN 수신기는 최대 10km 링크에서 100기가비트 이더넷 애플리케이션에 탁월한 성능을 제공합니다.

100G LR1 10km SFP-DD 광 트랜시버 RSD-100G-LR1

특징

응용 프로그램

메모:

1. KR-FEC는 선택 사항이며, 필요한 경우 당사에 문의하십시오.

그림 1. 모듈 블록 다이어그램

절대 최대 등급

| 매개변수 | 상징 | 민 | 맥스 | 단위 |

| 공급 전압 | Vcc | -0.3 | 다섯 | |

| 입력 전압 | 빈 | -0.3 | Vcc+0.3 | 다섯 |

| 보관 온도 | 티 | -20 | 85 | 섭씨 |

| 케이스 작동 온도 | 티씨 | 0 | 70 | 섭씨 |

| 습도(비응축) | Rh | 5 | 85 | % |

권장 작동 조건

| 매개변수 | 상징 | 민 | 전형적인 | 맥스 | 단위 |

| 공급 전압 | Vcc | 3.13 | 3.3 | 3.47 | 다섯 |

| 작동 케이스 온도 | 티씨 | 0 | 70 | 섭씨 | |

| 차선당 데이터 전송률 | fd | 106.25 | Gb/s | ||

| 습기 | Rh | 5 | 85 | % | |

| 전력 소모 | 오후 | 3 | 3.5 | W | |

| G.652와의 링크 거리 | 디 | 10 | km |

전기 사양

| 매개변수 | 상징 | 민 | 전형적인 | 맥스 | 단위 |

| 차동 입력 임피던스 | 진 | 90 | 100 | 110 | 옴 |

| 차동 출력 임피던스 | 주트 | 90 | 100 | 110 | 옴 |

| 차동 입력 전압 진폭1 | ΔVin | 1600 | mVp-p | ||

| 차동 출력 전압 진폭2 | ΔVout | 900 | mVp-p |

메모:

1. TxnP와 TxnN 사이의 차동 입력 전압 진폭을 측정합니다.

2. 출력 전압의 차동 진폭은 RxnP와 RxnN 사이에서 측정됩니다.

광학적 특성

| 매개변수 | 상징 | 민 | 전형적인 | 맥스 | 단위 | 메모 |

| 송신기 | ||||||

| 중심 파장 | λc | 1304.5 | 1317.5 | 나노미터 | ||

| 측면 모드 억제 비율 | SMSR | 30 | dB | |||

| 평균 발사력 | 입을 삐죽 내밀기 | -1.4 | 4.5 | dBm | ||

| 송신기 및 분산 아이 클로저(TDECQ) | TDECQ | 3.4 | dB | |||

| 멸종 비율 | 응급실 | 3.5 | dB | |||

| OFF 송신기의 평균 발사 전력 | -30 | dB | ||||

| 수화기 | ||||||

| 중심 파장 | λc | 1304.5 | 1317.5 | 나노미터 | ||

| OMA 외부에서의 수신기 감도 | RXsen | -6.1 | dBm | 1 | ||

| 평균 수신 전력 | 핀 | -7.7 | 4.5 | dBm | ||

| 수신기 반사율 | -26 | dB | ||||

| LOS 어설트 | -13 | dBm | ||||

| LOS 디어서트 – OMA | -11 | dBm | ||||

| LOS 히스테리시스 | 0.5 | dB | ||||

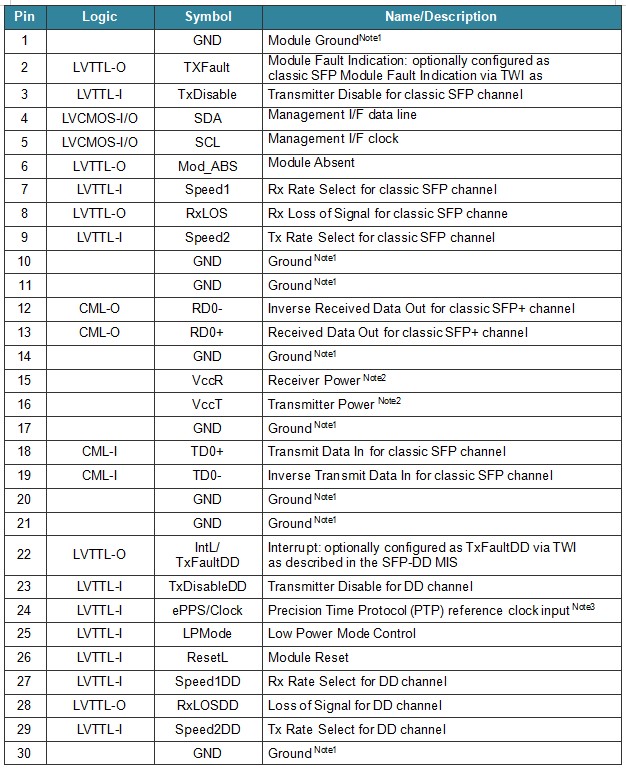

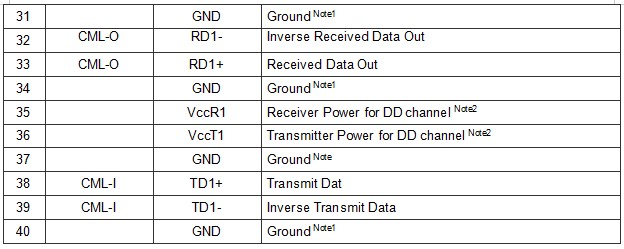

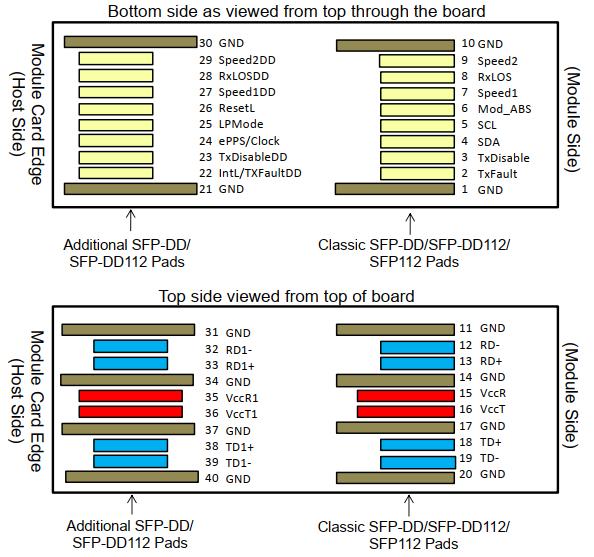

핀 설명

메모:

1. SFP-DD는 모든 신호와 전원 공급에 공통 접지(GND)를 사용합니다. SFP-DD 모듈 내의 모든 접지는 공통이며, 별도의 언급이 없는 한 모든 모듈 전압은 이 공통 접지를 기준으로 합니다. 이들을 호스트 보드의 신호 공통 접지면에 직접 연결하십시오.

2. VccR, VccT는 동시에 인가되어야 하며, VccR1, VccT1도 동시에 인가되어야 합니다. 호스트 측에 대한 요구 사항이 정의되어 있습니다. 커넥터의 Vcc 핀은 각각 최대 1000mA의 전류를 견딜 수 있도록 정격되어 있습니다.

3. ePPS 핀(사용하지 않는 경우)은 호스트에서 50Ω 접지로 종단 처리할 수 있습니다.

그림 2. 전기 핀 배치 상세 정보

속도1, 속도2, 속도1DD, 속도2DD

Speed1, Speed2, Speed1DD 및 Speed2DD는 모듈 입력이며 모듈 내 30kΩ 이상의 저항을 통해 GND에 풀다운됩니다. Speed1은 채널 1의 광 수신 신호 속도를 선택적으로 지정합니다. Speed1DD는 채널 2의 광 수신 신호 속도를 선택적으로 지정합니다. Speed2는 채널 1의 광 송신 신호 속도를 선택적으로 지정합니다. Speed2DD는 채널 2의 광 송신 신호 속도를 선택적으로 지정합니다.

참고: 128 GFC 버전부터 FC LSN은 더 이상 Speed1, Speed2, Speed1DD 및 Speed2DD 신호를 사용할 필요가 없으며, 이러한 신호를 프로그래밍 가능 기능이나 다른 용도로 재활용하는 방안을 검토 중입니다.

리셋L 핀

리셋. LPMode_Reset 모듈에는 내부 풀업 저항이 있습니다. ResetL 핀에 최소 펄스 길이(t_Reset_init)보다 긴 시간 동안 로우 레벨이 유지되면 모듈이 완전히 리셋되어 모든 사용자 모듈 설정이 기본 상태로 돌아갑니다. 모듈 리셋 어서트 시간(t_init)은 ResetL 핀의 로우 레벨이 해제된 후 상승 에지에서 시작됩니다. 리셋 실행(t_init) 동안 호스트는 모듈이 리셋 인터럽트 완료를 나타낼 때까지 모든 상태 비트를 무시해야 합니다. 모듈은 Data_Not_Ready 비트가 반전된 IntL 신호를 출력하여 이를 나타냅니다. 전원을 켤 때(핫 인서트 포함) 모듈은 리셋 없이도 리셋 완료 인터럽트를 출력합니다.

모드_ABS

Mod_ABS는 호스트 보드에서 Vcc Host에 풀업되어야 하고, 모듈 내부에서는 로우로 풀업되어야 합니다. Mod_ABS는 모듈이 삽입되면 "로우" 상태가 됩니다. 모듈이 호스트 커넥터에서 물리적으로 분리되면 호스트 보드의 풀업 저항으로 인해 Mod_ABS는 "하이" 상태가 해제됩니다.

LP모드

LPMode는 호스트에서 입력되는 신호로, 액티브 하이 로직으로 동작합니다. SFP-DD/SFP-DD112 모듈에서 LPMode 신호는 Vcc로 풀업되어야 합니다. 호스트는 LPMode 신호를 통해 SFP-DD/SFP-DD112 모듈이 SFP-DD 관리 사양에 정의된 대로 소프트웨어에서 고전력 모드로의 전환을 활성화할 때까지 저전력 모드를 유지할지 여부를 정의할 수 있습니다. 저전력 모드(LPMode 신호가 로우로 비활성화된 경우)에서는 관리 인터페이스가 초기화된 후 모듈이 즉시 고전력 모드로 전환될 수 있습니다.

리셋L

ResetL 신호는 모듈에서 Vcc로 풀업되어야 합니다. ResetL 신호가 최소 펄스 길이(t_Reset_init)보다 오랫동안 낮은 레벨을 유지하면 모듈이 완전히 초기화되어 모든 사용자 모듈 설정이 기본 상태로 돌아갑니다.

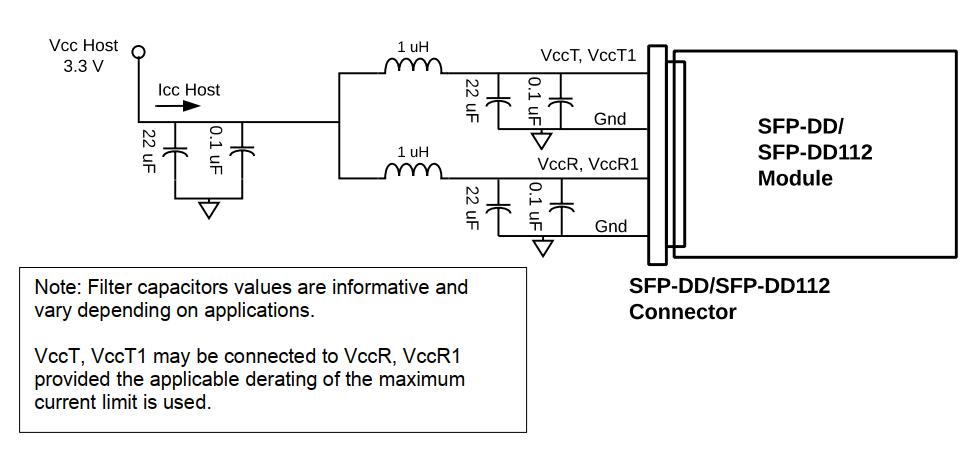

전원 공급 필터링

호스트 보드는 그림 3에 표시된 전원 공급 필터링을 사용해야 합니다.

그림 3. 호스트 보드 전원 공급 필터링

진단 모니터링 인터페이스(선택 사항)

달리 명시되지 않는 한, 다음의 디지털 진단 특성은 정상 작동 조건을 기준으로 정의됩니다.

| 매개변수 | 상징 | 민 | 맥스 | 단위 | 메모 |

| 온도 모니터 절대 오차 | DMI_Temp | -3 | +3 | 섭씨 | 작동 온도 범위 |

| 공급 전압 모니터 절대 오차 | DMI _VCC | -0.1 | 0.1 | 다섯 | 전체 작동 범위에 걸쳐 |

| 채널 RX 전력 모니터 절대 오차 | DMI_RX_Ch | -2 | 2 | dB | 1 |

| 채널 바이어스 전류 모니터 | DMI_Ibias_Ch | -10% | 10% | 엄마 | |

| 채널 TX 전력 모니터 절대 오차 | DMI_TX_Ch | -2 | 2 | dB | 1 |

참고:

1. 서로 다른 단일 모드 광섬유의 측정 정확도로 인해 +/-1dB의 추가적인 변동이 발생할 수 있으며, 전체 정확도는 +/-3dB의 오차 범위 내에 있을 수 있습니다.

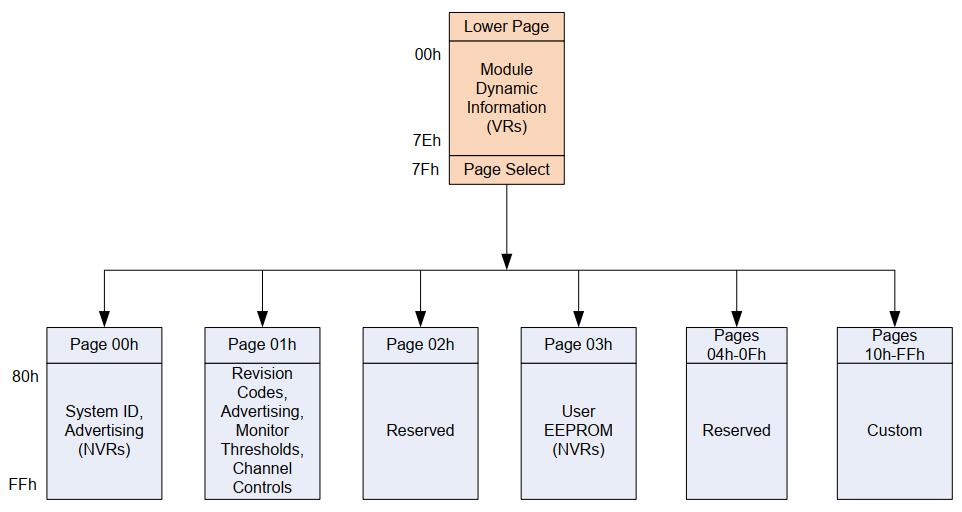

SFP-DD MIS에 명시된 대로 디지털 진단 기능은 I2C 인터페이스를 통해 사용할 수 있습니다. SFP-DD MIS 관리 메모리는 그림 4에 나와 있습니다.

8비트 주소 체계로 인해 호스트가 직접 접근할 수 있는 관리 메모리는 256바이트로 제한되며, 이는 하위 메모리(주소 00h~7Fh)와 상위 메모리(주소 80h~FFh)로 나뉩니다.

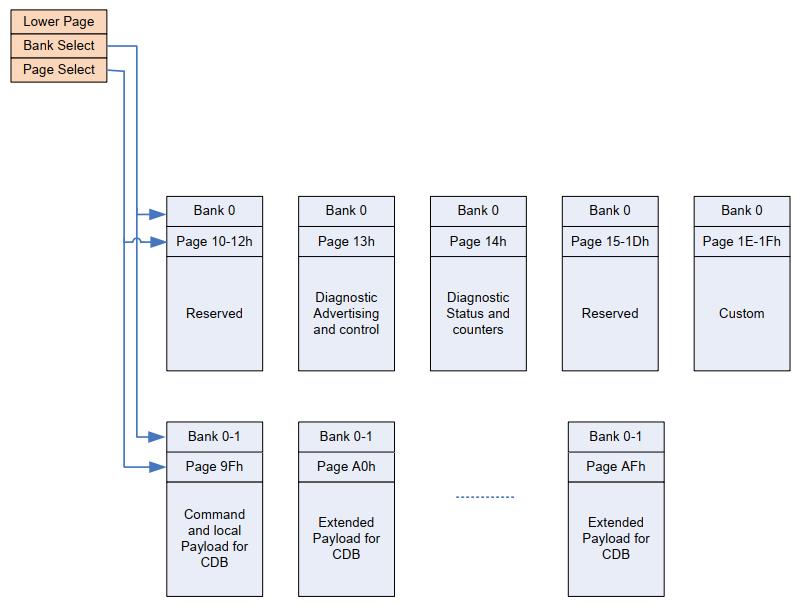

추가 내부 관리 메모리1의 주소 지정 구조는 그림 5에 나와 있습니다.

모듈 내부의 관리 메모리는 호스트가 항상 접근할 수 있는 128바이트 크기의 단일 주소 공간(하위 메모리)과 각각 128바이트 크기의 여러 상위 주소 서브스페이스(페이지)로 구성되며, 이 중 하나만 상위 메모리에서 호스트가 볼 수 있도록 선택됩니다. 동일한 페이지 번호를 가진 페이지들이 여러 개 존재하는 경우(예: 동일한 페이지 번호를 가진 페이지들이 여러 개 있는 경우)에는 두 번째 단계의 페이지 선택이 가능합니다.

이 구조는 수동형 구리 모듈용 256바이트 평면 메모리를 지원하며, 플래그 및 모니터와 같은 하위 메모리 주소에 신속하게 접근할 수 있도록 합니다. 시리얼 ID 정보 및 임계값 설정과 같이 시간적 중요도가 낮은 항목은 하위 페이지의 페이지 선택 기능을 통해 접근할 수 있습니다. 더 복잡한 모듈처럼 더 많은 관리 메모리가 필요한 경우에는 호스트가 필요에 따라 다양한 페이지를 호스트에서 접근 가능한 상위 메모리 주소 공간으로 동적으로 매핑해야 합니다.

참고: 관리 메모리 맵은 호스트와 모듈 간의 시간 제약적인 상호 작용을 가능하게 하면서 메모리 크기를 확장할 수 있도록 페이지와 뱅크를 사용하는 CMIS 메모리 맵을 기반으로 설계되었습니다. 이 메모리 맵은 단 두 개의 전기 레인만 수용하고 필요한 메모리 용량을 제한하기 위해 변경되었습니다. QSFP에서 볼 수 있는 것과 같은 단일 주소 지정 방식이 사용됩니다.

그림 4. QSFP28 메모리 맵

그림 5. SFP-DD MIS 은행 페이지 메모리 맵

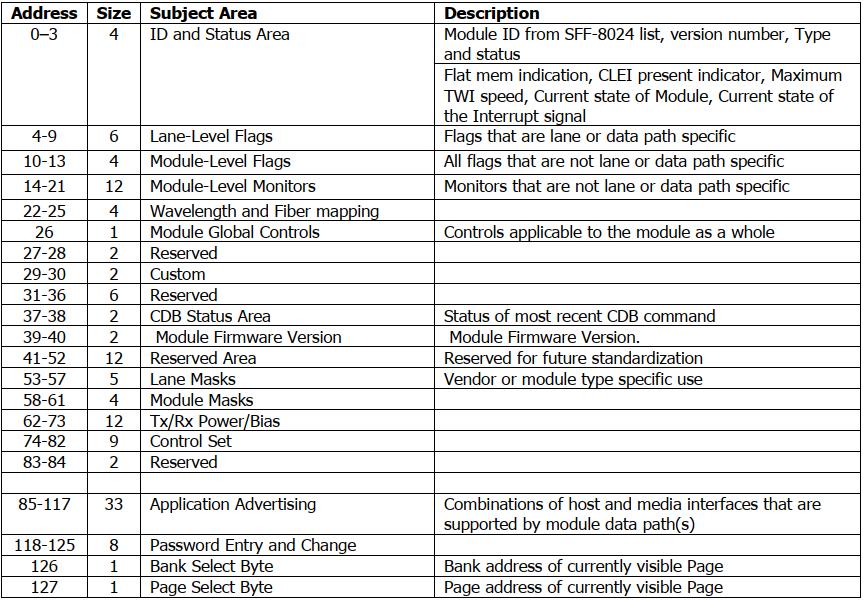

그림 6. 하위 메모리 개요

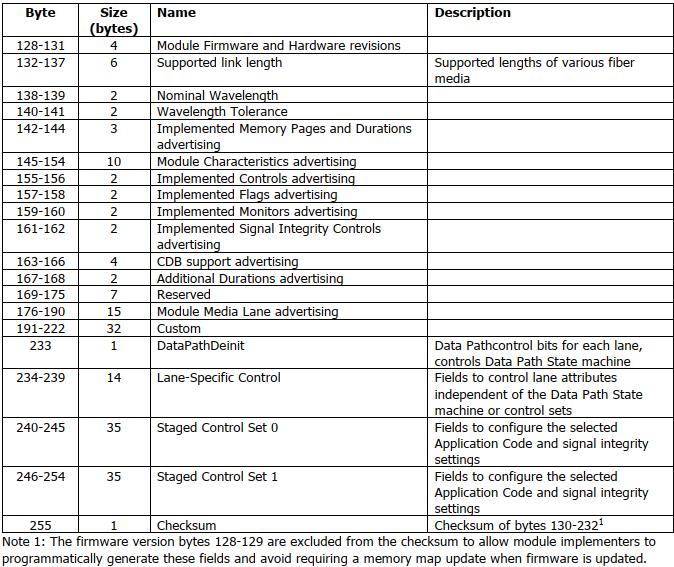

그림 7. 페이지 00h 메모리 개요

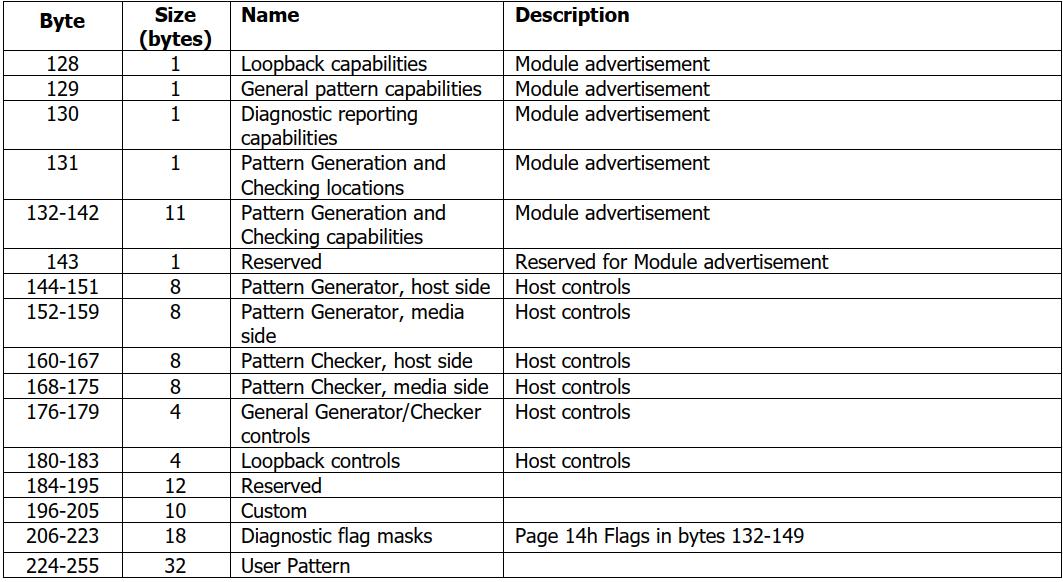

그림 8. 1페이지 메모리 개요

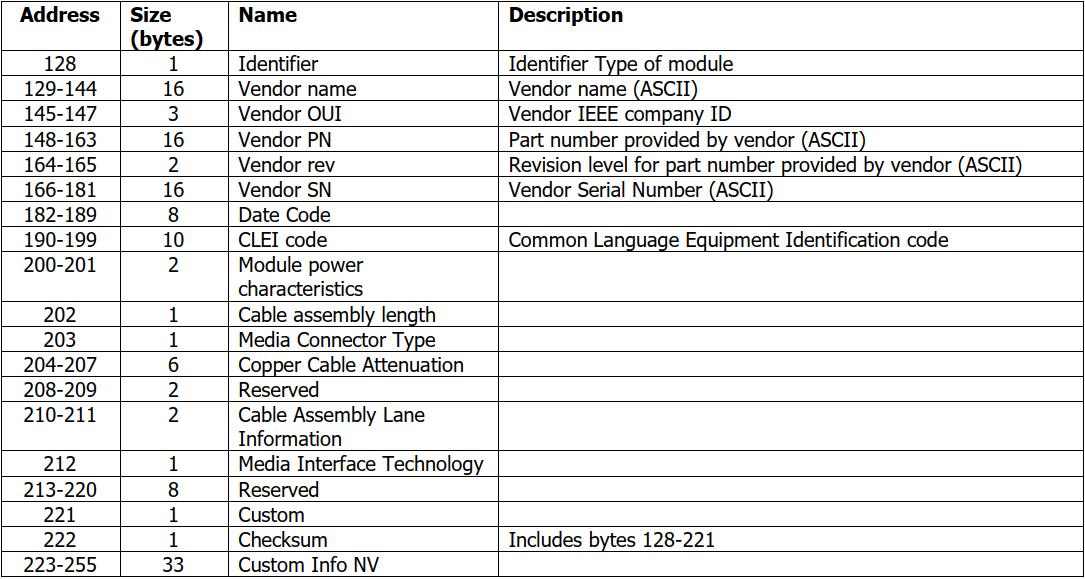

그림 9. 13페이지 메모리 개요

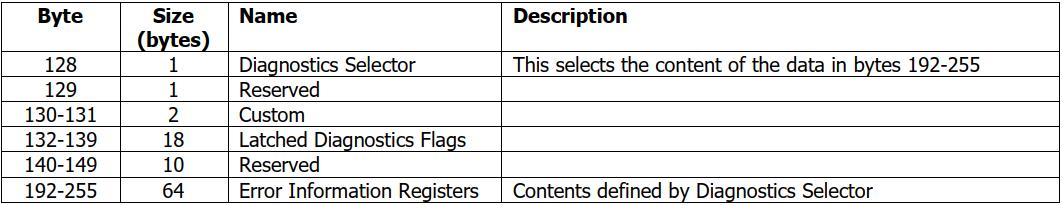

그림 10. 14페이지 메모리 개요

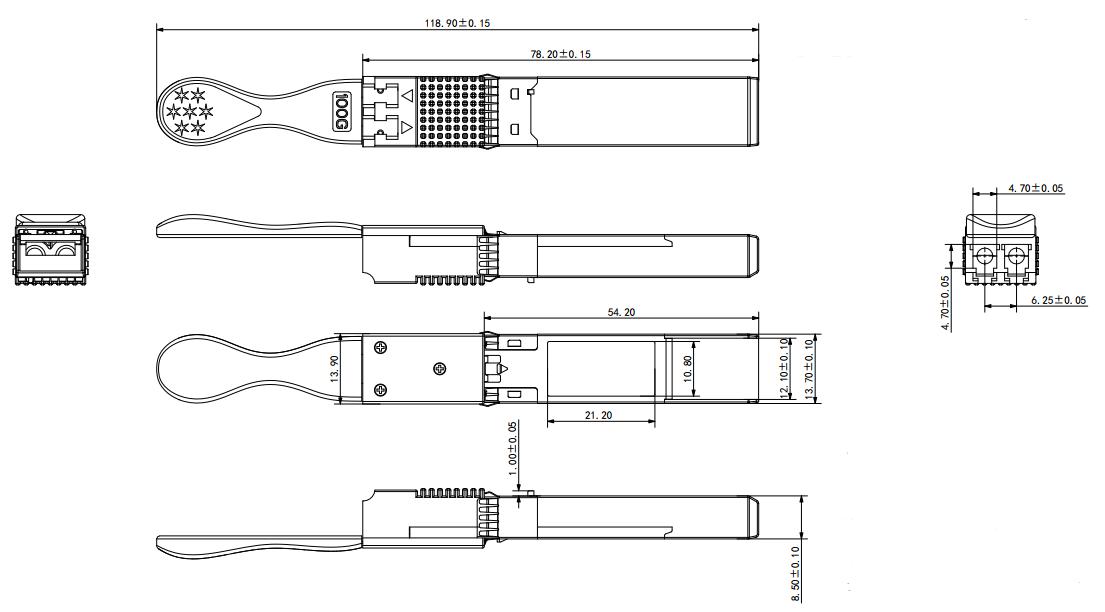

기계적 치수

그림 11. 기계적 사양

참고 자료

1. SFP-DD MSA

2. IEEE802.3cu 100GBASE-LR1

3. 100G 람다 MSA 100G LR1-10

주문 정보

| 부품 번호 | 제품 설명 |

| RSD-100G-LR1 | SFP56-DD LR1, 106.25Gb/s, 10km, EML+PIN, SMF, 듀얼 LC |

이 제품에 대해 알고 싶으신가요?

IF 우리의 제품에 관심이 있으시고 자세한 내용을 알고 싶습니다. 여기에 메시지를 남겨주세요, 우리는 최대한 빨리 당신을 회신 할 것입니다.